Shift-Left Verification: Early IC Design Reliability

Shift-left verification embeds automated analysis into IC design, finding vulnerabilities early, reducing costs, and accelerating time-to-market in mobile, AI, and consumer electronics. Reliability and efficiency are key.

After the preliminary infractions are fixed or waived, developers can just disable gray boxing and wage useful simulation and format jobs, keeping efficiency throughout iterative combination.

By flagging such concerns instantly after schematic capture– specifically as block-level and IP assimilation happens– designers close voids well prior to useful simulation. This not just stops parasitic leak and power-down failings yet additionally aesthetics gadget aging and system instability, paving the way for positive progression to layout.

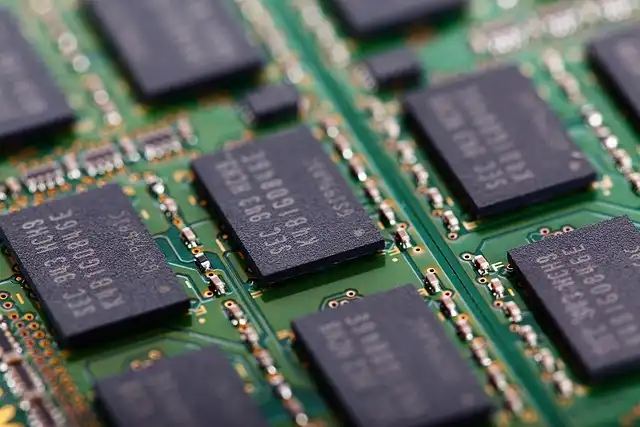

The Growing Complexity of IC Design

Today’s AI-driven mobile and consumer electronics markets require IC designers to provide even more capability in much less space, all while meeting limited power and reliability constraints. As layouts move listed below the 2 nm node and integrate countless power domains, both technological and organization risks multiply. Designers encounter the twin challenge of developing complicated systems within pressed project timelines– where late mistake discovery can imply missed out on due dates or costly respins.

Adopting a Shift-Left Verification Approach

To address these realities, a shift-left verification frame of mind is obtaining traction throughout the semiconductor sector. Instead of delegating complete reliability checks to the end of the flow, shift-left strategies focus on recognizing vulnerabilities and style mistakes at the earliest practical phase. By embedding automated pre-simulation analysis right into schematic assimilation, teams can swiftly situate problems when they are fastest– and most affordable– to take care of.

For non-repetitive or custom-made designs, grey boxing supports thorough evaluations of connection, flagging reliability issues such as missing degree shifters or leakage in between power domain names.

Traditional verification methods– developed around post-layout simulation and schematic sign-off– simply can not stay on par with the speed and intricacy of next-generation layouts. The moment and calculate price of simulating every possible circumstance is excessive, and the threat of missing out on uncommon or context-dependent problems climbs with each new assimilation.

Gray Boxing: Early Structural Interface Analysis

Among the useful ways to bring shift-left checks to schematic combination is through “gray boxing.” This method lets designers preserve and examine the structural user interface between blocks prior to running useful simulation. For non-repetitive or custom-made designs, grey boxing sustains extensive evaluations of connectivity, flagging dependability problems such as missing out on level shifters or leakage between power domains.

Such devices can change traditional electrical policy check (ERC) flows, delivering much better coverage in drastically less time. For large, CPU-scale jobs, pre-simulation analysis can be finished in under an hour– compared to the months often needed to reach insurance coverage with standard full-chip simulation.

Benefits of Pre-Simulation Analysis

Join us as we discover the story behind Nordic’s leap right into the PMIC space, explore what makes these little powerhouses so essential, and find how Nordic’s ingenious PMIC profile is establishing brand-new criteria on the market.

“Partner Material”

permits today’s industry assumed leaders to share their one-of-a-kind understanding and point of view with the

better ASPENCORE target market. Product released as “Companion Material” was produced by or in support of ASPENCORE’s companion( s).

along with the ASPENCORE Workshop team and may not show the sights of the site and editors to which it is published.For.

even more info on this program, email.

support@aspencore.com.

A device like Understanding Analyzer, with its automatic analysis, clear GUI, and comprehensive circuit acknowledgment, provides quantifiable benefits not simply for dependability, but also for general style velocity and project ROI.

As layouts move listed below the 2 nm node and incorporate countless power domains, both technological and organization threats multiply. Rather than delegating comprehensive integrity checks to the end of the circulation, shift-left methods concentrate on identifying susceptabilities and layout errors at the earliest practical phase. By installing automated pre-simulation analysis right into schematic combination, teams can promptly situate issues when they are fastest– and most inexpensive– to deal with.

Whether released in analog, mixed-signal or digital flows, these techniques reinforce not just IC designs yet likewise an organization’s ability to satisfy market requirements promptly and effectively. Worldwide of reducing nodes and expanding expectations, changing left is the smart step for layout honesty and service success.

This early-and-often technique implies developers can prioritize fixing systemic dangers, not simply regional violations, and can share significant offense summaries with partners– further speeding up team-wide debug and closure.

Installing shift-left techniques in the verification circulation repays beyond technological correctness. The savings from early problem recognition drive faster time-to-market, a vital advantage in consumer-driven sections like mobile and AI-enabled devices. Preventing late-stage respins not only reduces expenses yet directly improves the competition and online reputation of layout teams.

Early Detection’s Impact on Time-to-Market

Avoiding late-stage respins not only decreases costs but straight enhances the competitiveness and credibility of style groups.

1 early detection2 IC design

3 pre-simulation analysis

4 reliability

5 shift-left verification

6 time-to-market

« Microsoft’s Mu: Efficient AI for Windows 11VPNs for Wyoming Pornhub Ban: Privacy & Access »